|

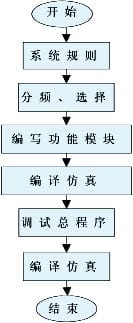

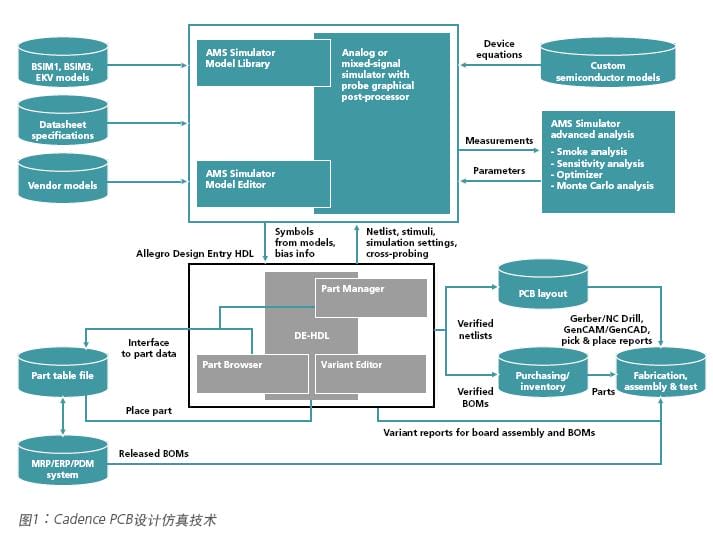

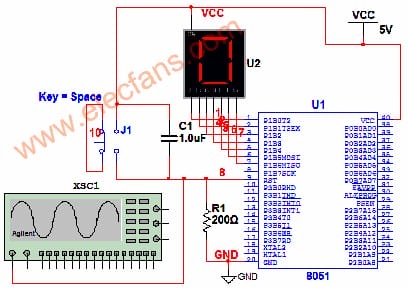

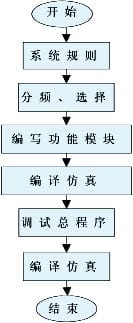

ЁЁЁЁв§бд ЁЁЁЁаХКХДЋЪфвЛАуПЩЗжЮЊСНДѓВПЗжЃКБрТыгыНтТыЁЃЦфжаБрТывЊЧѓИљОнЫљДЋЪфаХКХЬиЕубЁдёКЯЪЪЕФБрТыЗНЪНЁЃгЩгкВЛЭЌЕФаХКХдкВЛЭЌЕФЛЗОГжаНјааДЋЪфЃЌЪмЕНЕФИЩШХЪЧВЛЭЌЕФЃЌЖјбЁдёКЯЪЪЕФБрТыЗНЗЈПЩвдзюДѓЯоЖШЕФБмУтИЩШХЃЌЪЙЭЈаХИќМгЫГГЉЁЂИќМгзМШЗЁЃ ЁЁЁЁвЊЪЕЯжВЛЭЌЕФБрТыЗНЪНЙиМќЪЧвЊевЕНКЯЪЪЕФЫуЗЈЃЌВЂЧввЊЧѓЫуЗЈБиаыМђНрврМцШнЁЃБЪепдкетРяжївЊВЩгУСЫЖдБШЁЂСЊКЯКЭФЃПщЛЏЕФЩшМЦЗНЗЈЃЌЪЙУПвЛжжБрТыГЩЮЊвЛИіЖРСЂФЃПщЃЌЕЋгжЙВгУЭЌвЛИіЛђЖрИіЪБжгЁЃгЩДЫЃЌДѓДѓНкдМСЫГЬађЕФДцДЂПеМфЃЌМѕЩйСЫГЬађЕФЕїЪдЪБМфЁЃ ЁЁЁЁЮФеТНЋгУVHDLЩшМЦАЫжжГЃгУЕФБрТыЗНЪНЃЌВЂдЫгУALTERAЙЋЫОЕФQUARTUSIIЩшМЦШэМўНјааЗТецЕїЪдЁЃQUARTUSIIЩшМЦШэМўЪЧвЛПюПЊЗХЁЂгыНсЙЙЮоЙиЁЂЖрЦНЬЈЁЂЭъШЋМЏГЩЛЏЁЂЗсИЛЕФЩшМЦПтЁЂФЃПщЛЏЙЄОпЁЂжЇГжИїжжHDLЁЂгаЖржжИпМЖБрГЬгябдНгПкЕФЗЧГЃЯШНјЕФEDAЙЄОпШэМўЁЃСэЭтЃЌГЌИпЫйгВМўУшЪігябдVHDLОпгаЧПДѓЕФгябдНсЙЙЁЂЖрВуДЮЕФУшЪіЙІФмЁЂСМКУЕФвЦжВадКЭПьЫйЕФASICзЊЛЛФмСІЃЌжЇГжгВМўЕФЩшМЦЁЂзлКЯЁЂбщжЄКЭВтЪдЁЃвђДЫЃЌгІгУVHDLЩшМЦЭЈаХБрТыВЈаЮОпгаживЊвтвхЁЃ ЁЁЁЁзмЬхЗНАИЩшМЦ ЁЁЁЁЗНАИзмЬхЩшМЦШчЭМ1ЫљЪОЁЃЪзЯШЃЌдкдЫгУVHDLБраДГЬађЪББиаызёееЯЕЭГЙцдђЃЌАДееЯЕЭГПтКЏЪ§ЕїгУЃЌЗёдђБрвыНЋЛсВњЩњЮЪЬтЁЃЦфДЮЃЌПМТЧЕНЗжФЃПщБрГЬЃЌЖјУПвЛжжБрТыЗНЪНЕФБрГЬЛсгУЕНВЛЭЌЦЕТЪЕФЪБжгЃЌвђДЫвЊНЋЯЕЭГЪБжгЖўЗжЦЕЁЂЫФЗжЦЕКЭАЫЗжЦЕЃЌвдБИашвЊЁЃШЛКѓОЭЪЧвЊЩшМЦбЁдёФЃПщЃЌЗНБуЖдАЫжжБрТыЕФздгЩбЁдёЁЃдйНјаа ИїИіБрТыФЃПщЕФVHDLБрТыЃЌНјЖјПЩвдж№ИіБрвыЗТецЁЃзюКѓЃЌЕБУПвЛИіФЃПщБрвыЗТецЭЈЙ§КѓЃЌОЭЪЧвЊНЋУПвЛИіЖРСЂФЃПщГЬађећКЯдквЛЦ№ЃЌаЮГЩзмЕФБрТыГЬађЃЌВЂЧвЕїЪдзмГЬађЁЃ

ЭМ1 змЬхЩшМЦСїГЬЭМ ЁЁЁЁЕЅдЊФЃПщЩшМЦМАЕїЪд ЁЁЁЁЗжЦЕФЃПщ ЁЁЁЁЙЄзїдРэ ЁЁЁЁЫљЮНЗжЦЕЃЌОЭЪЧНЋвЛИіИјЖЈЦЕТЪНЯИпЕФЪ§зжЪфШыаХКХЃЌОЙ§ЪЪЕБЕФДІРэКѓЃЌВњЩњвЛИіЛђЪ§ИіЦЕТЪНЯЕЭЕФЪ§зжЪфГіаХКХЁЃЗжЦЕБОжЪЩЯЪЧМгЗЈЦїЕФБфЛЏЃЌЦфМЦЪ§жЕгЩЗжЦЕГЃЪ§N=fin/foutЃЈfinЪЧЪфШыЦЕТЪЃЌfoutЪЧЪфГіЦЕТЪЃЉОіЖЈЃЌЦфЪфГіВЛЪЧвЛАуМЦЪ§ЦїМЦЪ§НсЙћЃЌЖјЪЧИљОнЗжЦЕГЃЪ§ЖдЪфГіаХКХЕФИпЁЂЕЭЕчЦННјааПижЦЁЃ ЁЁЁЁШэМўЩшМЦ ЁЁЁЁЯТУцЩшМЦвЛИіЖдЪфШыЪБжгаХКХНјаа2ЗжЦЕЁЂ4ЗжЦЕКЭ8ЗжЦЕЕФЗжЦЕГЬађЁЃИљОнЪЕМЪашвЊЛЙПЩвдЩшМЦЗжЦЕЯЕЪ§ЮЊ2NЕФЗжЦЕЦїЃЌжЛашвЊЪЕЯжвЛИіФЃNЕФМЦЪ§ЦїЃЌдйАбФЃNЕФМЦЪ§ЦїЕФзюИпЮЛжБНгИЖИјЗжЦЕЦїЕФЪфГіаХКХЃЌМДПЩЕУЕНЫљашвЊЕФЗжЦЕаХКХЁЃ ЁЁЁЁЗжЦЕЯЕЪ§ЪЧ2ЕФећЪ§ДЮУнЕФХМЪ§ЗжЦЕЦїФЃПщЭМШчЭМ2ЫљЪОЁЃ

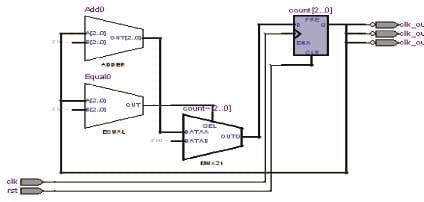

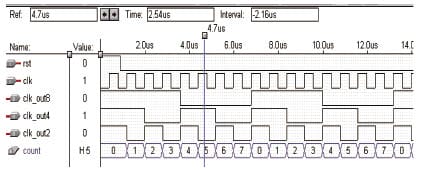

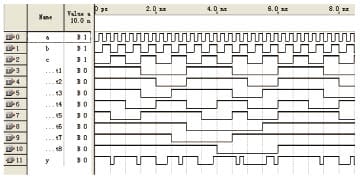

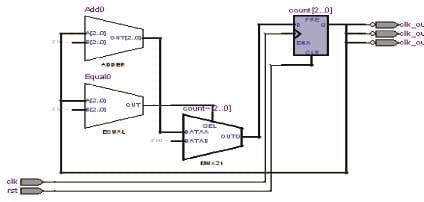

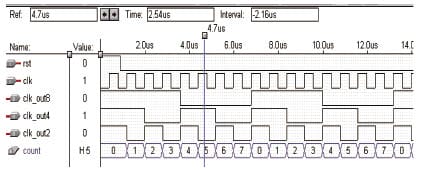

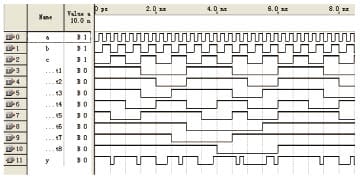

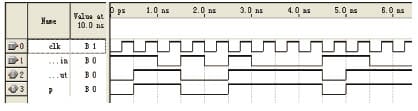

ЭМ2 2ЁЂ4ЁЂ8ЗжЦЕЦїЕФRTLФЃПщЭМ ЁЁЁЁДЫГЬађжаrstЮЊЕЭЕчЦНгааЇЃЌШєЪЕЯж2ЗжЦЕЕчТЗдђЪфГізюИпгааЇЮЛcount(0)ЃЌ4ЗжЦЕЕчТЗЪфГізюИпгааЇЮЛcount(1)ЃЌвРДЮРрЭЦЃЌ8ЗжЦЕЪфГізюИпгааЇЮЛcount(2)ЁЃ ЁЁЁЁдкMAX-plusIIЛЗОГжаБрвыЗТецВЈаЮШчЭМ3ЫљЪОЁЃ

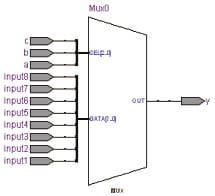

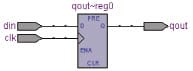

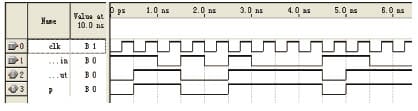

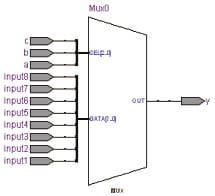

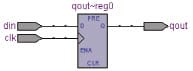

ЭМ3 2ЁЂ4ЁЂ8ЗжЦЕВЈаЮ ЁЁЁЁбЁдёФЃПщ ЁЁЁЁЙЄзїдРэ ЁЁЁЁДЫФЃПщЪЧгУгкбЁдёаХКХЕФЃЌзїгУОЭЪЧЕБЪфШыЖрТЗаХКХЪБЃЌжЛбЁШЁЦфжавЛТЗЪфГіЃЌЦфбЁдёвРОнЪЧИљОнЦфЕижЗЯпЕФаХКХЃЌЕижЗЯпгаNЬѕЃЌОЭФмжЦзї2NбЁвЛбЁдёЦїЁЃ ЁЁЁЁШэМўЩшМЦ ЁЁЁЁИљОнбЁдёФЃПщЕФЙЄзїдРэЃЌгІгУVHDLБраДЕФбЁдёЦїФЃПщЭМШчЭМ4ЫљЪОЁЃ

ЭМ4 бЁдёЦїЕФФЃПщЭМ ЁЁЁЁбЁдёЦїГЬађдкQUARTUSIIЛЗОГжаБрвыЗТецВЈаЮШчЭМ5ЫљЪОЁЃ

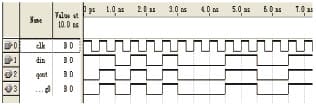

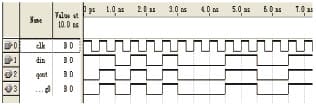

ЭМ5 бЁдёЦїВЈаЮ ЁЁЁЁЙІФмФЃПщ ЁЁЁЁNRZ-LЃЈВЛЙщСуТыЃЉ ЁЁЁЁNRZ-L(ЦН)ТыЮоТлЪЧ“1”ЛЙЪЧ“0”ЪБЃЌЯрСкТыдЊЕчЦНМЋадОљВЛИФБфЃЌМДдк4ЗжЦЕЕФЪБжгclkЩЯЩ§биЫцЪфШыаХКХdinБфЛЏЖјЪфГіаХКХencoder-outЁЃ ЁЁЁЁОпЬхVHDLФЃПщЭМШчЭМ6ЫљЪОЁЃ

ЭМ6 NRZ-L(ЦН)ЕФФЃПщЭМ ЁЁЁЁГЬађдкQUARTUSIIЛЗОГжаБрвыЗТецВЈаЮШчЭМ7ЫљЪОЁЃ

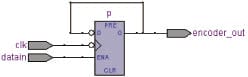

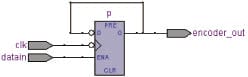

ЭМ7 NRZ-LТыВЈаЮ ЁЁЁЁNRZ-M(аХКХВюЗжТы) ЁЁЁЁNRZ-MаХКХВюЗжТыЃЌЕБЮЊ“1”ЪБЯрСкТыдЊЕчЦНМЋадИФБфЃЌ“0”ЪБЯрСкТыдЊЕчМЋадВЛИФБфЃЌМДдкЪБжгclkЮЊ4ЗжЦЕЕФЩЯЩ§бигіЪфШыаХКХdatain “1”ЖјЬјБфЃЌ“0”БЃГжЪфГіаХКХencoder-outЁЃ ЁЁЁЁОпЬхVHDLФЃПщЭМШчЭМ8ЫљЪОЁЃ

ЭМ8 NRZ-MЃЈаХКХВюЗжТыЃЉЕФФЃПщЭМ ЁЁЁЁГЬађдкQUARTUSIIЛЗОГжаБрвыЗТецВЈаЮШчЭМ9ЫљЪОЁЃ

ЭМ9 NRZ-MТыВЈаЮ ЁЁЁЁNRZ-SЃЈПеИёВюЗжТыЃЉ ЁЁЁЁNRZ-SЃЈПеИёВюЗжТыЃЉЃЌЕБЮЊ“0”ЪБЯрСкТыдЊЕчЦНМЋадИФБфЃЌ“1”ЪБЯрСкТыдЊЕчМЋадВЛИФБфЃЌМДгыNRZ-M(аХКХВюЗжТы)ЧЁКУЯрЗДЃЌclkЮЊ4ЗжЦЕЁЃ ЁЁЁЁОпЬхVHDLФЃПщЭМШчЭМ10ЫљЪОЁЃ

|