|

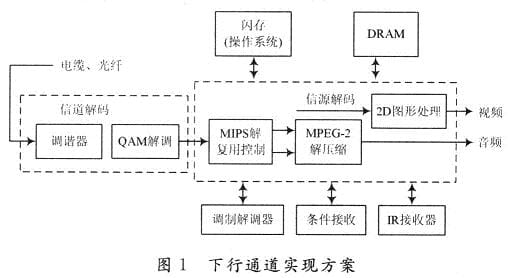

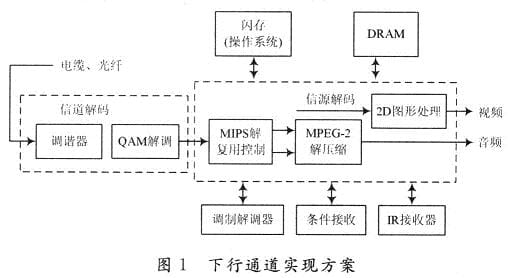

����0 �� �� �������������������ֶ�ý��ҵ���Internet�����Ѹ�ٷ�չ���������ֻ����п�����Ч�����ҹ�������ߵ���������Դ�������Ƶ�㲥�����ֵ��ӵĽ��ռ�����Internet���ۺ�ҵ���ܡ� ����1 ���ֻ�����������Ʒ��� �������ֻ����з�Ϊ����ͨ��������ͨ���������Ե��»���˵����ߵ����źţ�����ͨ������ӿͻ��˵��������˵�ָ� ��������ͨ��������ͼ1��ʾ����г�����������������ĸ�Ƶ�źţ�ͨ��QAM���������ŵ����룬���ز��з��������������Ƶ������������Ϣ�Ĵ�����(TS)����������һ��������������Ƶ����һЩ������Ϣ���⸴�������������ֲ�ͬ�Ľ�Ŀ����ȡ��Ӧ��������Ƶ����������������MPEGһ2����������Ӧ�Ľ������������������Ϣ�Ļ�ԭ�����ڸ��ѵ��ӣ���������ģ���������Ƶ��ʵʩ���ţ������ú���ʶ���û��ͽ��м��˹��ܵ����ܿ�����֤�Ϸ��û������տ���MPEGһ2���������������Ƶ�źŵĽ�ѹ��������Ƶ����������ƵD��A�任����ԭ��ģ��������Ƶ�źţ��ڳ����ɫ���ӻ�����ʾ������ͼ���ṩ��������������Ŀ��

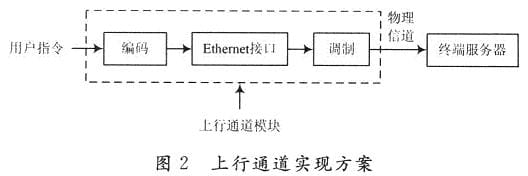

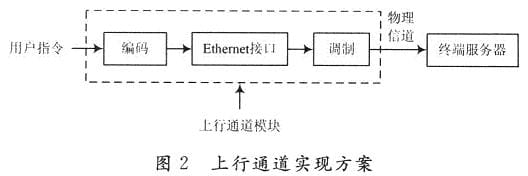

��������ͨ��������ͼ2��ʾ���û�����ָ�Ȼ�������������ͨ��Э�飬����̫���ӿڴ��䵽���������پ������ŵ������ն˷�������

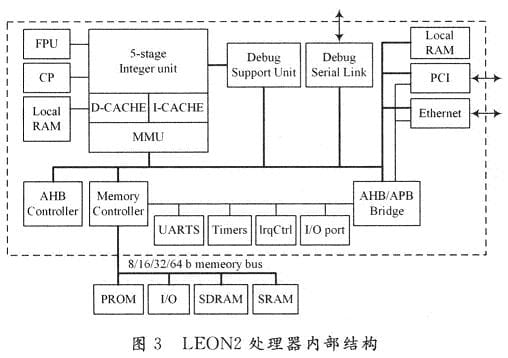

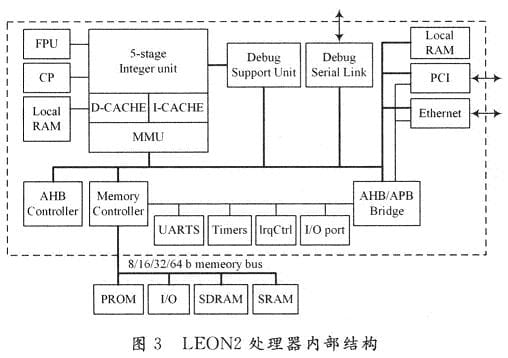

����2 LEON2������ ����Ƕ��ʽCPU�����ֵ��ӻ����е����࣬����������ŵ������Ժ�����Ҫ�⸴�ã��Ѵ������ֳ���Ƶ����Ƶ��ʹ��Ƶ����Ƶ�����ݷ��뿪��CPU��Ƕ��ʽ����ϵͳ������ƽ̨����Ҫ�����ϵͳһ����������������ʾ���������������չ�����ͼ�ĵ��ӽ��롢���ݽ��롢��Ƶ�źŵ����±任�ȹ��ܡ� ����LEONϵ��32λRISC�������˵ĵ�һ���汾��LEONl��������ŷ�����������ƿ����ġ�LEONl����Ƴ�����Ϊ��ʹŷ���ܹ������ں��պ��������Ƕ��ʽ�������϶�������������������Jiri CaislerΪ������Ŷ������LEONl���ŷ����ֶ���������������Gaisler Research��˾���������Ƴ���LE�DON2��������LEON2��һ�������õ��������ˣ�ʹ��SPARC V8ָ�������Դ�����ɿ��ۺϵ�VHDL���빹�ɡ�LEON2�ڲ��ṹ��ͼ3��ʾ��

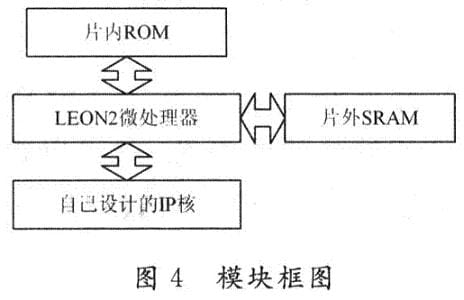

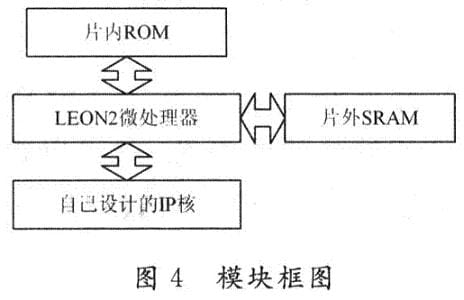

����LEON2������������Ԫ��5����ˮ����ƣ�����SPARC V8(IEEEһ1754)ָ�����ϵ�ṹ�����з��������Cache��ָ��Cache��LEON2��������Ԫ����һ����ѡ��16��16��MAC��Ԫ���ܹ���ɻ�����DSP���㣬ͬʱ���ṩ�˸������㵥Ԫ(FPU)�Ľӿں�Э������(CP)�Ľӿڣ�������չ���������DSP������LEON2ѡ����ARM��˾��AMBA 2��0Ƭ�����߱������������ڴ����������ʱ�����жϿ�������UART�ӿڡ�PCI�ӿڡ�10��100 Mb��s��̫���ӿڵ�ģ�顣LEON2ͬʱ���ṩ1������֧�ֵ�Ԫ��1�����Դ��ڣ�����֧��Ƭ�ڵ��ԡ�LEON2��һ���dz���Ҫ���ص���Ǿ��кܺõĿ������ԡ�ʹ���߸����Լ�����Ҫ��ͨ��һ����tcl��tk�ű���д��ͼ�λ����棬��LEON2�ں˵ľ������ģ��������ã������������Cache�Ĵ�С�ͷ��ʷ�ʽ���Ƿ�֧��Ӳ���ˣ��������Ƿ���Ҫ�ڴ档 ����Gaisler Research��˾���ṩ�˱Ƚ����ƵĻ���LEON2��GNU��������������ʹ���߿���ʹ��TSIM��GRMON����LEON�ں˵ĵ��Է��档 LECCS��ר�����LEON�Ľ������ϵͳ�����Խ���C��C++�ı���͵��ԡ�SnapGear Linux�ǻ���LClinux��ʵʱLinux�ںˣ�����LEON���ṩ�˶�LEON��������ȫ��֧�֣�����֧��MMU��NOM�DMU�Ȳ�ͬ���÷����� �����������������Կ�����LEON2����ǿ���Ӳ�����ú��걸��������������֧�֣����Գе����ֻ�����CPUҪ��ĸ����źŴ������� ����3 ��FPGA�������Ͻ���LEON2��SoCƽ̨ ����3��1 Ӳ��ƽ̨�Ľ��� ����ͼ4���ǻ���LEON2��ƽ̨��ģ���ͼ��LE�DON2��������Ϊ���IJ��֣�Ƭ��ROM���Monitor����ϵͳ��ʼ���ͽ�������Ƭ��SRAM�ڵ�����Ƭ��RAM��FPGA��������Memory��������ų�������ݡ���Ƶ�IP��ͨ��AHB���ߺ�LEON2�������

����FPGA��������Ҫ��������Դ��50 MHz��Դʱ�ӣ�1��Altera��˾�ĺ���FPGAоƬEP2C20F484һC8������Ԫ18 752����2Ƭ512 KB��IS61LV25616һAL SRAMоƬ���32 b����1 MB����������ÿƬ���Ϊ�ɼ���1 MB���ܹ��������䵽2 MB��JTAG�ӿ�(ͨ��JTAG�ӿڿ��Դ�PC���϶�EP2C20F484C8���б��)������������COMl�������������ڳ������ء� ���������úõ�LEON2��VHDL���룬������Ƶ�HDL���룬һ��ʹ��Synplify�ۺϹ�������FPGA�������ļ���Ȼ��ʹ��Quartus���в��ֲ��ߣ���LEON2��ͬƬ��ROM��Ƭ��SRAM���ӣ����ֲ�����ɺ�������Ӧ��SOF�ļ���ͨ��JTAG�˿ڽ�SOF�ļ����ص�Ƭ����ȥ����FPGAӲ���������ã����ռ��FPGA��Դ��5 800������Ԫ�����Դﵽ��ʱ��Ƶ�����Ϊ46 MHz��

|