|

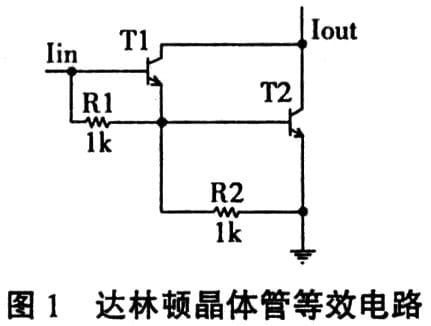

ЁЁЁЁМЦЫуЛњЯЕЭГЪЧгЩаэЖрОпгаЖРСЂЙІФмЕФФЃПщЛЅЯрСЌНгЖјГЩЕФЁЃЫцзХМЦЫуЛњЕФВЛЖЯЗЂеЙКЭЙуЗКгІгУЃЌИїЩњВњГЇЩЬГ§СЫЯђгУЛЇЬсЙЉећЬзЯЕЭГЭтЃЌЛЙЩшМЦКЭЬсЙЉИїжжЙІФмЕФВхМўФЃПщЃЌШУгУЛЇИљОнздМКЕФашвЊЙЙГЩздМКЕФгІгУЯЕЭГЛђРЉГфдгаЕФЯЕЭГЁЃетаЉФЃПщМфашвЊЛЅЯрЭЈаХЃЌашвЊгаИпЫйЁЂПЩППЕФаХЯЂНЛЛЛЭЈЕРЃЌетОЭЪЧзмЯпЁЃзмЯпЪЙЕУМЦЫуЛњИїФЃПщжЎМфЕФаХКХЯпПЩвджБНгЛЅЯрСЌНгЃЌЬсИпСЫаХКХДЋЪфЕФЫйЖШЁЃ ЁЁЁЁVHDL(Very-High-Speed Integrated Circuit Hardware Description Language)ЪЧвЛжжгВМўУшЪігябдЃЌдкЕчзгЩшМЦСьгђЕУЕНЙуЗКгІгУЃЌзюаТАцБОЮЊIEEEБъзМЕФ1076-1993АцЃЌгЩIEEEдк1993ФъЙЋВМЁЃVHDLжївЊгУгкУшЪіЪ§зжЯЕЭГЕФНсЙЙЁЂааЮЊЁЂЙІФмКЭНгПкЁЃБОЮФгУVHDLЕФгаЯозДЬЌЛњРДУшЪіКЭЗТецМЦЫуЛњзмЯпПижЦЦїЕФТпМааЮЊЁЃ ЁЁЁЁ1 змЯпдкзмЯпПижЦЦїЕФПижЦЯТЙЄзї ЁЁЁЁдкМЦЫуЛњЯЕЭГИїФЃПщжЎМфЕФаХЯЂЭЈаХЙ§ГЬжаЃЌУПвЛЪБПЬжЛФмгавЛзщаХЯЂдкзмЯпЩЯДЋЪфЁЃШчЙћгаЖрзщаХЯЂвЊДЋЪфЃЌжЛФмдкзмЯпПижЦЦїЕФПижЦЯТЃЌАДЫГађЗжБ№ДЋЪфЃЌетбљЖдУПвЛзщаХЯЂЕФДЋЪфОЭаЮГЩвЛИіДЋЪфжмЦкЃЌетИіжмЦкАќРЈЩъЧыЗжХфНзЖЮЁЂбАжЗНзЖЮЁЂЪ§ОнНЛЛЛНзЖЮКЭГЗЯћНзЖЮЁЃЩъЧыЗжХфНзЖЮгЩжїФЃПщЬсГізмЯпЪЙгУЩъЧыЃЌОзмЯпПижЦЦїХњзМКѓЛёЕУзмЯпЪЙгУШЈЃЛжЎКѓжїФЃПщАбДгФЃПщЕижЗЗХжУЕНЕижЗзмЯпЩЯЃЌМДбАжЗНзЖЮЃЛДгФЃПщНгЪеЕНЕижЗКѓзіКУЯргІЕФЭЈаХзМБИЙЄзїЃЌВЂгыжїФЃПщНЈСЂЭЈаХЃЌНјааЪ§ОнНЛЛЛЃЛЪ§ОнНЛЛЛНсЪјКѓЃЌжїФЃПщЭЈжЊзмЯпПижЦЦїЃЌВЂНЛЛЙзмЯпЪЙгУШЈЃЌМДГЗЯћНзЖЮЁЃГЃгУЕФзмЯпЭЈаХЗНЪНгаЭЌВНЭЈаХЗНЪНКЭвьВНЭЈаХЗНЪНСНжжЁЃ ЁЁЁЁ2 ЭЌВНЭЈаХЗНЪНЕФгаЯозДЬЌЛњУшЪіКЭЗТец ЁЁЁЁдкЭЌВНЭЈаХЗНЪНРяЃЌФЃПщжЎМфЕФЭЈаХДЋЪфжмЦкЪЧЙЬЖЈЕФЁЃгаОЋШЗЮШЖЈЕФЯЕЭГЪБжгзїЮЊДЋЪфжмЦкЕФЁАБъГпЁБЃЌЭЈаХЫЋЗНбЯИёАДееЪБжгБъГпНјааИїжжВйзїЃЌвджїФЃПщ(ШчCPU)ДгДгФЃПщ(ШчФкДц)ЖСШЁЪ§ОнЮЊР§ЃЌзмЯпПижЦЦїПђЭМШчЭМ1ЫљЪОЁЃ

ЁЁЁЁетжжЗНЪНЯТзмЯпЕФПижЦзДЬЌзЊвЦЭМШчЭМ2ЫљЪОЁЃ

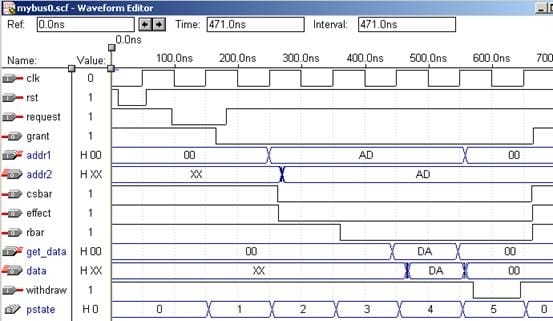

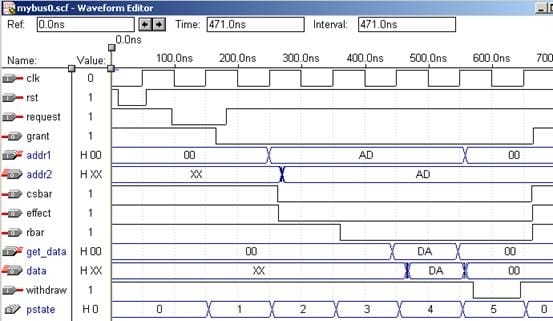

ЁЁЁЁгУVHDLНјааУшЪіВЂдкMAX+PLUSIIЩЯНјааЗТецЃЌНсЙћШчЭМ3ЫљЪОЃК

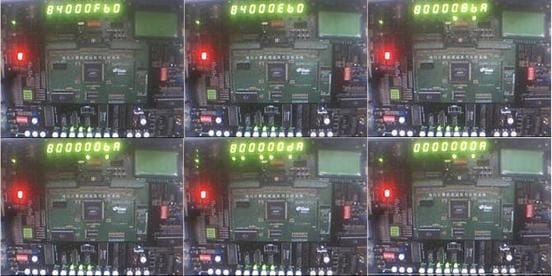

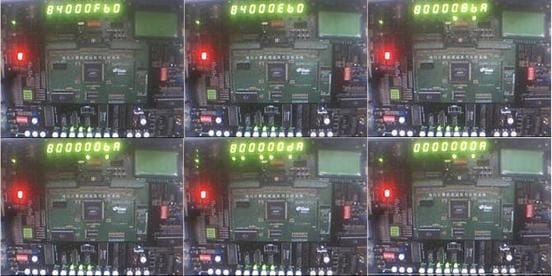

ЁЁЁЁДгЭМ3ПЩвдПДГіЃЌПижЦЦївЛПЊЪМДІгкзДЬЌ0(ПеЯазДЬЌ)ЃЌДЫЪБзмЯпХњзМПижЦаХКХgrantЁЂЦЌбЁаХКХcsbarЁЂЕижЗгааЇаХКХeffectКЭЖСПижЦаХКХrbarОљДІгкЮоаЇЕФИпЕчЦНЃЛвЛЕЉгажїФЃПщЗЂГізмЯпЧыЧѓЃЌМДrequestаХКХЮЊЕЭЕчЦНЃЌПижЦЦїзЊвЦЕНзДЬЌ1ЃЌзмЯпХњзМПижЦаХКХгааЇЃЌЩъЧыЕУЕНХњзМЃЌетРяМйЩшжїФЃПщжЛгавЛИіЃЌМДВЛДцдкЖрИіжїФЃПщОКељЪЙгУзмЯпЕФЧщПіЃЛНјШызДЬЌ2КѓЃЌжїФЃПщЗЂГіЕижЗЃЌетРяМйЩшЕижЗЮЊЁАADЁБЃЌЭЌЪБжУЦЌбЁаХКХcsbarКЭЕижЗгааЇаХКХeffectЮЊгааЇзДЬЌЃЌДгФЃПщНгЪеЕНЕижЗгааЇаХКХКЭЦЌбЁаХКХКѓЃЌИљОнжїФЃПщЗЂГіЕФЕижЗНјааЪ§ОнзМБИЙЄзїЃЛНјШызДЬЌ3КѓЃЌжїФЃПщЗЂГіЖСПижЦаХКХЃЌМДжУrbarаХКХЮЊгааЇзДЬЌЃЛНјШызДЬЌ4КѓЃЌМйЩшДгФЃПщЪ§ОнзМБИОЭаїЃЌВЂЗЂЫЭЕНЪ§ОнзмЯпЩЯЃЌетРяМйЩшЪ§ОнЮЊЁАDAЁБЃЌжїФЃПщЖСШЁЪ§ОнЃЛНјШызДЬЌ5КѓЃЌжїФЃПщЖСЪ§ОнЭъБЯЃЌЗЂГіГЗЯћаХКХЃЌМДжУwithdrawаХКХЮЊгааЇзДЬЌЃЌжЎКѓЗЕЛизДЬЌ0ЃЌЫљгаПижЦаХКХЖМЗЕЛиЕНЮоаЇзДЬЌЃЛжСДЫЃЌвЛИіЪ§ОнДЋЪфжмЦкНсЪјЁЃдкДЋЪфЙ§ГЬжаЃЌИїИіФЃПщЕФЖЏзїбЯИёАДееЯЕЭГЪБжгЭЌВННјааЁЃ ЁЁЁЁБОЩшМЦЯТдиЕНGW48ЈDGK2/PK2 EDAЪЕбщПЊЗЂЯЕЭГЃЌИУЯЕЭГФПБъаОЦЌЮЊEP1K100QC208-3ЃЌАДееНсЙЙЭМNo.0НјаагВМўВтЪдЃЌЪЕбщЯЕЭГЬсЙЉВтЪдв§НХЕФЯожЦЃЌжЛВтЪдЕижЗКЭЪ§ОнОљЮЊ4ЮЛ(ВтЪдЕЭ4ЮЛ)ЕФЧщПіЃЌНсЙћШчЭМ4ЫљЪОЁЃ

ЁЁЁЁДгЭМ4жаПЩвдПДГіЃЌдкзДЬЌ0ЃЌЪзЯШЩшжУwithdrawЁЂrequestКЭrstЮЊЁА1ЁБЃЌвРДЮЖдгІЭМжаЯТЗН3ИіЗЂЙтЖўМЋЙмЃЌДЫЪБ4ИіЪфГіПижЦаХКХrbarЁЂeffectЁЂcsbarКЭgrantЮЊЁА1ЁБЃЌет4ИіаХКХАДДЮађзщГЩвЛИі4ЮЛЖўНјжЦЪ§ОнЃЌИУЪ§ОнОЙ§выТыЦївыТыКѓгЩЪ§ТыЙмЯдЪОЪфГіНсЙћЃЌвђ4ИіаХКХОљЮЊЁА1ЁБЃЌЙЪгІИУЯдЪОНсЙћЁАFЁБЃЌШчЭМжаЩЯУцЕФЪ§ТыЙмЯдЪОЁАFЁБ(гвБпЕк3ИіЪ§ТыЙм)ЁЃЕк2ВНЃЌАДееЭМ3ЫљЪОЪБађЩшжУrstКЭrequestаХКХВЂгЩАДМќ3ЪфШывЛИіЪБжгТіГхЃЌНјШызДЬЌ1ЃЌДЫЪБgrantаХКХЮЊЁА0ЁБЃЌ4ИіЪфГіПижЦаХКХзщКЯЮЊЁА1110ЁБЃЌПЩвдПДЕНЭМжаЪ§ТыЙмЯдЪОЁАEЁБЃЌБэУїжїФЃПщЩъЧызмЯпБЛХњзМЁЃЕк3ВНЃЌЩшжУЕижЗаХКХaddr1(ЕЭ4ЮЛ)ЮЊЁА1010ЁБЃЌМДЁАAЁБЃЌШчЭМжаЪ§ТыЙмЯТЗНСНИіЗЂЙтЖўМЋЙмЫљЪОЃЌВЂЪфШывЛИіЪБжгТіГхЃЌНјШызДЬЌ2ЃЌИУЕижЗаХКХгЩaddr2ОвыТыЦївыТыКѓгЩЪ§ТыЙмЯдЪОГіРДЃЌШчЭМжаЩЯУцзюгвБпЕФЪ§ТыЙмЯдЪОЁАAЁБЃЌдкИУзДЬЌжаЕижЗгааЇаХКХeffectКЭЦЌбЁаХКХcsbarОљЮЊЁА0ЁБЃЌДЫзДЬЌЯТжїФЃПщЗЂГіЕижЗгааЇаХКХКЭЦЌбЁаХКХЃЌ4ИіЪфГіПижЦаХКХзщКЯЮЊЁА1000ЁБЃЌДгЭМжаПЩвдПДЕНЪ§ТыЙмЯдЪОЪ§зжЁА8ЁБЁЃЕк4ВНЃЌЪфШывЛИіЪБжгТіГхНјШызДЬЌ3ЃЌИУзДЬЌЯТжїФЃПщЗЂГіЖСПижЦаХКХЃЌМДжУrbarаХКХЮЊЁА0ЁБЃЌ4ИіЪфГіПижЦаХКХШЋВПЮЊЁА0ЁБЃЌШчЭМжаЪ§ТыЙмЯдЪОЁА0ЁБЁЃЕк5ВНЃЌЩшжУЪ§ОнаХКХget_data(ЕЭ4ЮЛ)ЮЊЁА1101ЁБЃЌМДЁАDЁБЃЌШчЭМжаЪ§ТыЙмЯТЗНСНИіЗЂЙтЖўМЋЙмЫљЪОЃЌВЂЪфШывЛИіЪБжгТіГхЃЌНјШызДЬЌ4ЃЌИУЪ§ОнаХКХгЩdataОвыТыЦївыТыКѓгЩЪ§ТыЙмЯдЪОГіРДЃЌШчЭМжаЩЯУцгвБпЕк2ИіЪ§ТыЙмЯдЪОЁАdЁБЁЃЕк6ВНЃЌЪфШывЛИіЪБжгТіГхЃЌНјШызДЬЌ5ЃЌжїФЃПщЖСШЁЪ§ОнЭъБЯЃЌВЂЗЂГіГЗЯћаХКХЃЌ1ИіЪ§ОнДЋЪфжмЦкНсЪјЃЛжЎКѓШчЙћдйЪфШывЛИіЪБжгТіГхдђЛиЕНзДЬЌ0ЁЃ

|