引言

信号传输一般可分为两大部分:编码与解码。其中编码要求根据所传输信号特点选择合适的编码方式。由于不同的信号在不同的环境中进行传输,受到的干扰是不同的,而选择合适的编码方法可以最大限度的避免干扰,使通信更加顺畅、更加准确。

要实现不同的编码方式关键是要找到合适的算法,并且要求算法必须简洁亦兼容。笔者在这里主要采用了对比、联合和模块化的设计方法,使每一种编码成为一个独立模块,但又共用同一个或多个时钟。由此,大大节约了程序的存储空间,减少了程序的调试时间。

文章将用VHDL设计八种常用的编码方式,并运用ALTERA公司的QUARTUSII设计软件进行仿真调试。QUARTUSII设计软件是一款开放、与结构无关、多平台、完全集成化、丰富的设计库、模块化工具、支持各种HDL、有多种高级编程语言接口的非常先进的EDA工具软件。另外,超高速硬件描述语言VHDL具有强大的语言结构、多层次的描述功能、良好的移植性和快速的ASIC转换能力,支持硬件的设计、综合、验证和测试。因此,应用VHDL设计通信编码波形具有重要意义。

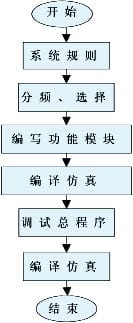

总体方案设计

方案总体设计如图1所示。首先,在运用VHDL编写程序时必须遵照系统规则,按照系统库函数调用,否则编译将会产生问题。其次,考虑到分模块编程,而每一种编码方式的编程会用到不同频率的时钟,因此要将系统时钟二分频、四分频和八分频,以备需要。然后就是要设计选择模块,方便对八种编码的自由选择。再进行 各个编码模块的VHDL编码,进而可以逐个编译仿真。最后,当每一个模块编译仿真通过后,就是要将每一个独立模块程序整合在一起,形成总的编码程序,并且调试总程序。

图1 总体设计流程图

单元模块设计及调试

分频模块

工作原理

所谓分频,就是将一个给定频率较高的数字输入信号,经过适当的处理后,产生一个或数个频率较低的数字输出信号。分频本质上是加法器的变化,其计数值由分频常数N=fin/fout(fin是输入频率,fout是输出频率)决定,其输出不是一般计数器计数结果,而是根据分频常数对输出信号的高、低电平进行控制。

软件设计

下面设计一个对输入时钟信号进行2分频、4分频和8分频的分频程序。根据实际需要还可以设计分频系数为2N的分频器,只需要实现一个模N的计数器,再把模N的计数器的最高位直接付给分频器的输出信号,即可得到所需要的分频信号。

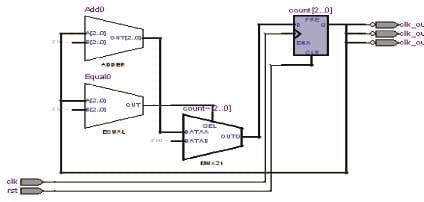

分频系数是2的整数次幂的偶数分频器模块图如图2所示。

图2 2、4、8分频器的RTL模块图

此程序中rst为低电平有效,若实现2分频电路则输出最高有效位count(0),4分频电路输出最高有效位count(1),依次类推,8分频输出最高有效位count(2)。

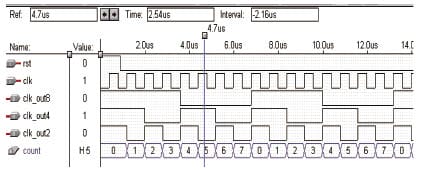

在MAX-plusII环境中编译仿真波形如图3所示。

图3 2、4、8分频波形

选择模块

工作原理

此模块是用于选择信号的,作用就是当输入多路信号时,只选取其中一路输出,其选择依据是根据其地址线的信号,地址线有N条,就能制作2N选一选择器。

软件设计

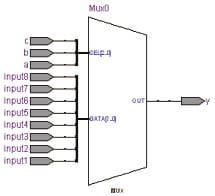

根据选择模块的工作原理,应用VHDL编写的选择器模块图如图4所示。

图4 选择器的模块图

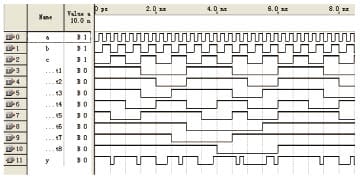

选择器程序在QUARTUSII环境中编译仿真波形如图5所示。

图5 选择器波形

功能模块

NRZ-L(不归零码)

NRZ-L(平)码无论是“1”还是“0”时,相邻码元电平极性均不改变,即在4分频的时钟clk上升沿随输入信号din变化而输出信号encoder-out。

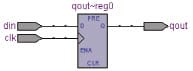

具体VHDL模块图如图6所示。

图6 NRZ-L(平)的模块图

程序在QUARTUSII环境中编译仿真波形如图7所示。

图7 NRZ-L码波形

NRZ-M(信号差分码)

NRZ-M信号差分码,当为“1”时相邻码元电平极性改变,“0”时相邻码元电极性不改变,即在时钟clk为4分频的上升沿遇输入信号datain “1”而跳变,“0”保持输出信号encoder-out。

具体VHDL模块图如图8所示。

图8 NRZ-M(信号差分码)的模块图

程序在QUARTUSII环境中编译仿真波形如图9所示。

图9 NRZ-M码波形

NRZ-S(空格差分码)

NRZ-S(空格差分码),当为“0”时相邻码元电平极性改变,“1”时相邻码元电极性不改变,即与NRZ-M(信号差分码)恰好相反,clk为4分频。

具体VHDL模块图如图10所示。